# 会社概要

| 会社名             | 株式会社プライムゲート                                                                                                                                            |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 設立              | 1995年10月                                                                                                                                               |  |

| 資本金             | 1億9000万円                                                                                                                                               |  |

| 代表取締役社長         | 梅田 芳直                                                                                                                                                  |  |

| 社員数             | 25名(エンジニア20名)(2019年07月現在)                                                                                                                              |  |

| 所在地             | 本社 〒755-0153 山口県宇部市床波1丁目6番13号                                                                                                                          |  |

| ウェブサイト          | http://www.prime-gate.com/                                                                                                                             |  |

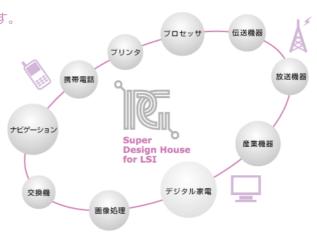

| 業務内容            | ASIC/FPGAの回路設計、EDAツール販売、IP販売、<br>アプリケーションソフト開発                                                                                                         |  |

| 取扱品目            | SystemC, Verilog-HDL, VHDL, Visual Basic, Visual C/C++                                                                                                 |  |

| 主要納入先<br>(回路開発) | ソニー株式会社、パナソニック株式会社、株式会社東芝、<br>日本電気株式会社、富士通株式会社、シャープ株式会社、<br>株式会社JVCケンウッド、富士ゼロックス株式会社、<br>住友重機械工業株式会社、オリンパスメディカルシステムズ株式会社、<br>ルネサスエレクトロニクス株式会社(順不同、敬称略) |  |

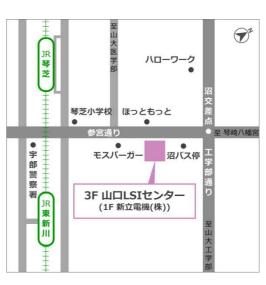

# アクセスマップ

### [山口本社]

JR床波駅より徒歩2分

#### [東京LSIセンター]

都営大江戸線・東京メトロ日比谷線 新御徒町駅 A4番出口より徒歩8分

都営浅草線 蔵前駅 A3番出口より徒歩10分

#### [山口LSIセンター]

JR琴芝駅 より徒歩15分 JR東新川駅 より徒歩17分

#### [大阪LSIセンター]

地下鉄御堂筋線 本町駅 8番出口より徒歩2分 地下鉄四つ橋線 本町駅 26番出口より徒歩2分 地下鉄中央線 本町駅 17番出口より徒歩3分

# プライムゲートとは

# 次代のLSI設計を担う "匠のエンジニア集団"、プライムゲート

限界を超え続け発展するエレクトロニクスの世界。プライムゲートは、LSIの更なる需要を見据え、1995年に設立されました。徹底的な設計管理体制が実現する「高品質」「短納期」にこだわったLSI開発は、クライアントから高い評価を受けています。

### IT社会の"頭脳"を創り出していきます。

株式会社プライムゲートは 1999年11月2日、ISO9001の 認証を取得いたしました。

### 社長メッセージ

### 世界最大のASICを提供し続けるために

半導体が世界に現れ数十年、今や私たちの生活は半導体によって支えられていると言っても過言ではありません。ムーアの法則に従い、LSIの物理的な集積度は継続的に上昇を続け、既にその集積度の向上に回路設計が追いつかない、いわゆる設計崩壊が始まっていると言われています。

われわれプライムゲートは創業以来、一貫してこのムーアの法則の最前線で戦ってきました。創業から3年後の1998年、当時某国では一年半かけて設計した50万ゲートの電話交換機のLSI、私達はその倍の100万ゲートを、たった3ヶ月で設計しました。それから数年後の現在、業界標準では6ヶ月かかる100万ゲートのASICを私達は2ヶ月で設計しています。

技術の進歩は、これからもLSIの集積度を上げ続けるでしょう。しかし、 世界最大規模のASICを生み出すのは、これからもプライムゲートであり続 けたい。これが私の願いです。

これからも、プライムゲートの活躍にご期待ください。

# PRIMEGATE Ltd.

# 技術と実績でクライアントの幅広いニーズに応えます。 ASIC/FPGA受託設計

お客様の要求仕様に応じたASICやFPGAの受託設計を行っています。 要求仕様のコンサルティング・作成から論理検証まで、いずれの範囲から でもお受けいたします。

| お客様I/F   |             | プライムゲート受託業務 ※常駐開発可       |

|----------|-------------|--------------------------|

| システム仕様   | <b>&gt;</b> | コンサルティング 要求仕様設計          |

|          |             | ▼                        |

| 機能要求仕様書  | ⊩           | 回路仕様設計                   |

|          |             | ▼                        |

| 試験要求仕様書  | ⊩           | 試験仕様設計                   |

|          |             | ▼                        |

| Cモデル、RTL | ⊩           | C/SystemCモデリング HDLコーディング |

|          |             | ▼                        |

|          |             | 論理検証                     |

|          |             | ▼                        |

|          |             | 論理合成 ゲートレベル検証            |

|          |             |                          |

- □ 要求仕様をまとめる時間がない!

- → 弊社のエンジニアが、打合せやホワイトボードを用いた説明等を元に、 形になっていないところからまとめ上げます!

- □ 昔作った回路を修正したいが、設計仕様書がなく手が付けられない・・・

- → 弊社では、貴社や第三者が過去資産として残っているRTLを解析し、 レポートにまとめ、必要に応じて修正を行うことが可能です!

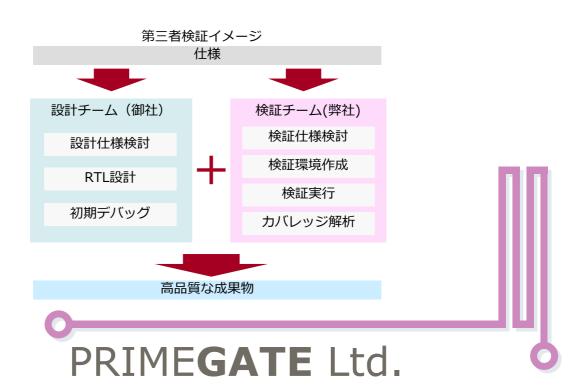

- □ 設計は問題なく終わるが、検証工数が増大し、みんな疲弊している・・・ → プライムゲートでは、第三者検証も請け負っております!

# ○ パートナーソーシングのご提案/ お客様の声

### "パートナーソーシング"のご提案

アウトソーシングではなくパートナーソーシング

We are on the same boat!

クライアント企業様と同じ船に乗り 同じ目的地を目指す仲間 = パートナーでありたい。 私たちはいつもそう考えています。

そして スペシャリストとしての経験と能力で いち早く確実に 目的地に到達することに貢献します。

わたしたちプライムゲートを、 御社の船の乗組員 = クルーにぜひ加えてください。

### お客様の声

- ✓ 一度プライムゲートの仕事を見た後では、 他の協力会社の仕事が見劣りしてしまう。

- ✓ 検証能力が高く、ピンポイントで問題点を指摘してくれる。

- ✓ 改善提案を出してくれるのがありがたい。

- ✓ 進捗状況の報告がタイムリーで適切。 何ができていて、何ができていないか、 どこまで進んでいるのか、明確に分かる。

- ✓ 仕事が速い。よくこの短納期で仕上げてくれた。

- ✓ 技術者としての暗黙知が共有されているので、 ツーカーで仕事ができる。

- ✓ 少ない、整理されていない情報で仕様書を書き上げてくれる 能力には驚いた。

- ✓ より上流の構想段階から一緒にやりたい。

# 設計実績:画像/音声系・1

規格別設計実績:画像/音声系・1

| 分類   | 規格/方式            | キーワード                                                                                                                                                                                                                                                     |

|------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 圧縮伸張 | MPEG2-TS         | MPEG2-TS Mux/DeMux処理,<br>スタートコード検出, MeP, MM, HW-e                                                                                                                                                                                                         |

|      | MPEG2-ES, 422@HL | スタートコード解析, 自動デコード,<br>422/420対応, アフィン変換, カメラ入力,<br>MeP, MM, PM                                                                                                                                                                                            |

|      | MPEG2, IEEE1394  | MPEG2コーデック, SoC, TX49, MeP, MM                                                                                                                                                                                                                            |

|      | MPEG4            | モバイル機器用MPEG4コーデック                                                                                                                                                                                                                                         |

|      | H.264            | CAVLC, CABAC, VC-1, VLC                                                                                                                                                                                                                                   |

| 画像処理 | 自然画像処理           | 下地検知, 下地除去, 誤差拡散、<br>格子パターン生成, 空間フィルター,<br>マスキング処理, エリア分割, 鏡像,<br>色ゴースト補正領域指定, イメージシフト,<br>リピート処理, 色ゴースト補正領域指定,<br>イメージシフト, リピート処理,<br>画像処理フィルタ(空間フィルタ/誤差拡散/<br>エッジ強調/階調補正/彩度補正),<br>HWEモデル, MPIツール,<br>デモスキートフィルタ,<br>デブロッキングフィルタ,<br>画像フィルタ処理、I2C制御、γ処理 |

| LCD他 | LCD/CRT          | LCD/CRTコントローラー                                                                                                                                                                                                                                            |

|      | LCD              | γ変換, 逆γ変換, LCD制御, A/D制御, RSDS,<br>LVDS, オーバードライブ, 黒挿入,<br>テストパタン発生                                                                                                                                                                                        |

|      | VIS, SD          | Host I/F, AudioDSP I/F,<br>CPU Serial通信制御                                                                                                                                                                                                                 |

|      | I2C, USB, CCD    | I2C制御, USB制御, CCD制御                                                                                                                                                                                                                                       |

|      | TSMF方式           | スクランブルサポート回路, VBID回路,<br>SYNC補正回路, UART(16550),<br>MPEG複数TSパケット処理                                                                                                                                                                                         |

| 音声   | AES/EBU          | DSP, S/P, P/S, SDRAM制御,<br>タイミング生成                                                                                                                                                                                                                        |

|      | I2S              | Inter-IC Sound                                                                                                                                                                                                                                            |

|      | SPDIF            | Sony-Philips Digital InterFace                                                                                                                                                                                                                            |

# 設計実績:画像/音声系・2

規格別設計実績:画像/音声系・2

| 分類        | 規格/方式                                                                                                                                        | キーワード                                          |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| TV/<br>映像 | NTSC, PAL, PAL-M, SECAM,<br>CGMS, WSS, Closed Caption,<br>TeleText, Macrovision,<br>4K2K,8K4K,QFHD,HD,<br>Camera Bayer,<br>On Screen Display | NTSC, PALビデオエンコーダ                              |

|           | HDTV,<br>ARIB STD-B4(VITC),<br>SMPTE RP168,188,196(VITC)                                                                                     | SDTV→HDTVアップコンバータ                              |

|           | SMPTE293M,<br>296M ITUR BT1358,<br>SMPTE RP188                                                                                               | フォーマット変換,<br>2:3,3:2プルダウン, SDRAM制御,<br>タイミング生成 |

|           | JPEG、NTSC、HDTV,<br>SD:SMPTE 272M/HD:SMPTE                                                                                                    | SDRAMコントローラ,<br>DDR2-SDRAM制御                   |

|           | IEC DV規格                                                                                                                                     | JPEG圧縮伸長                                       |

|           | YUV/YCbCr                                                                                                                                    | 画像合成・拡大縮小,独自フォーマット,<br>画像圧縮/伸張, SDRAMインタフェース   |

|           | IEEE1394経由IIDC,<br>ITU-R規格BT656                                                                                                              | RGB<=>YCbCr変換                                  |

|           | 画像調整                                                                                                                                         | アルファブレンド、OSD                                   |

# 設計実績:通信/伝送系・1

規格別設計実績:通信/伝送系・1

| 分類           | 規格/方式                                           | キーワード                                                                    |

|--------------|-------------------------------------------------|--------------------------------------------------------------------------|

| АТМ          | ATM, ALL                                        | OAMセル                                                                    |

|              | UTOPIA<br>(Level1, Level2)                      | ATMの回線・VPシェーピング                                                          |

|              | LTM-SWB, UTOPIA,<br>POS-PHY                     | LTM-SWB間INF<->UTOPIA,<br>POS-PHYINFフォーマット変換                              |

|              | I.431a                                          | 上位ATM回線DMUX,<br>下位ATM回線MUX                                               |

|              | ECHONET                                         | ARM, MAC/PHY                                                             |

|              | 16FETA, 8S3LA, 4S12LA,<br>OC3c/STM1, OC12c/STM4 | LTMPIUの各種制御                                                              |

| QoS          | QoS, トークン制御, MII                                | 帯域保証, チェイン構造メモリ管理,<br>経路切替, FCRAMインタフェース<br>帯域保証                         |

| イーサ          | イーサネット                                          | GbitEther                                                                |

| ネット          | ECHONET                                         | CRC, UART, I2C                                                           |

|              | S3MII, GMII                                     | Ether多重化処理, VLAN, MDIO,<br>FCS, STACKING, エラー検出,<br>タイミング制御, FV          |

|              | STM-0, 50MOIF                                   | PN生成・検査, SOH制御, LED制御,<br>P/S制御, S/P制御, パリティチェック                         |

|              | XGMII                                           | Ether多重化処理, VLAN, MDIO, FCS                                              |

|              | XAUI                                            | 10Gbpsインタフェース                                                            |

|              | FastEthernet, SERDES                            | FastEthernet-SERDES間I/F                                                  |

| E1/T/<br>SDH | E1/T1, PLL                                      | E1/T1マッピング・デマッピング,<br>フォーマット変換, 前詰め処理・削除,<br>ST,CALM多重, 速度変換,<br>FTS挿入検出 |

|              | SDH                                             | SDH, SRAM, フォーマット変換,<br>クロスコネクト                                          |

|              | SoNET/SDH/oHTR, FEC,<br>スクランブル/デスクランブル          | ReadSolomonエンコード/デコード, PN                                                |

# 設計実績:通信/伝送系・2、 CPUペリフェラル

規格別設計実績:通信/伝送系・2

| 分類           | 規格/方式                                              | キーワード                                                                 |

|--------------|----------------------------------------------------|-----------------------------------------------------------------------|

| LVDS         | LVDS (LVTTL)                                       | 76.8MbpsLVTTL, 614.4MbpsLVDS変換,<br>PN生成, PN照合, フレーム位相調整,<br>P/S,S/P変換 |

| CDMA         | W-CDMA                                             | HSDPA-Layer2(リオーダリング、<br>ディスアセンブリー、デサイファー),<br>CDMA                   |

|              | 3GPP                                               | DSPブート処理, C6805I/F                                                    |

|              | HSDPA方式                                            | HSDPA, 逆拡散, MatchedFilter, DSP-IF, I/QデータLVDS変換, DTCH/PRACHモード        |

| Pro-<br>MPEG | Pro-MPEG Code of Practice (#3 release 2 July 2004) | FEC (Forward Error Correction)                                        |

|              | Pro-MPEG Code of Practice<br>(#4 release 1 July)   | FEC (Forward Error Correction)                                        |

| 暗号           | AES                                                | Advanced Encryption Standard                                          |

|              | Kasumi                                             | 3GPP携帯電話                                                              |

規格別設計実績: CPUペリフェラル

| 分類  | 規格/方式                    | キーワード                                                                                             |

|-----|--------------------------|---------------------------------------------------------------------------------------------------|

| ARM | AMBA2.0                  | ARM9, APB, AHB, AXI,DMAC, TIMER,<br>AHB2AHBバスブリッジ, AHB-ARBITER,<br>Buster-Flashメモリ, NAND-Flashメモリ |

|     | AMBA3.0/4.0              | ARM11, MEMCONT, LPDDR4                                                                            |

|     | ARM BUS                  | ARM_BUS制御,<br>DDR SDRAM制御/M-DDR SDRAM制御,<br>SH-CPUの周辺回路, I2C I/F,<br>MPEG2CODEC用FIFO I/F          |

| その他 | MeP core, TX49 core      | MeP HWE                                                                                           |

|     | RS232C                   | PIOI/F, 8MバスI/F, SRAM制御,<br>SDRAM制御, OSDC制御                                                       |

|     | OCP (Open Core Protocol) | インターコネクト、周辺IF                                                                                     |

# 設計実績:IP系、制御系

規格別設計実績:IP系

| 分類 | 規格/方式            | キーワード                          |

|----|------------------|--------------------------------|

| IP | NAND-FLASH (PHY) | PHY                            |

|    | SDRAM (PHY)      | DDR3-SDRAM, DDR4-SDRAM         |

|    | MIPI             | PHY, Unipro                    |

|    | Unipro (1.8)     | データリンク層(Layer1.5)、RMMI         |

|    | SATA             | 送受信データ制御、キャッシュ機能               |

|    | PCI/PCIe         | 送受信データ制御、規格準拠                  |

|    | FILTER           | 空間、ベクトル、動き検出、奥行き生<br>成、クラスタリング |

|    | バスブリッジ           | バス変換、バッファリング                   |

|    | MMU、DMA          | アドレス変換、バス調停                    |

### 規格別設計実績:制御系

| 分類 | 規格/方式         | キーワード                                       |

|----|---------------|---------------------------------------------|

| 制御 | ATAPI, CAN    | SH3, SH4, ADPCMIF, DMA, TIMER, UART         |

|    | PCI, BasicI/O | SPAM制御, PCI IP, A/D,D/A制御,<br>PLL制御, タイマー制御 |

|    | メモリ制御         | ラインメモリ制御, カウンタ                              |

|    | SCSI, ECC     | SCSI I/F, ECC I/F, ライトバック                   |

|    | コントローラ制御      | DDR-SDRAMコントローラ, プリント<br>I/F,簡易データ圧縮        |

|    | メモリースティック     | メモリースティック制御                                 |

|    | ソフトウェア        | Nios II ファームウェア, USB I/Fチップ<br>利用           |

# 問題解決事例

プライムゲートには、様々なお客様との業務で培った 「技術力」「コミュニケーションカ」「適応力」「提案力」、 そして「誠実さ」と「高品質・短納期へのこだわり」があります。

次は、お客様の「困った」を解決させて下さい。

|      | お客様の課題                                                                                           | 弊社の解決事例                                                                                                          |

|------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 仕様検討 | 要求仕様がまとまらず、プロジェクトのスタートが遅れる。<br>あるいは、要求仕様がまとまらず、不安を抱えながらプロジェクトがスタートする。                            | プロジェクトに携わる中心メ<br>ンバーに対するヒアリングや<br>ミーティングにより、数日で<br>仕様をまとめ上げました。                                                  |

| 設計   | 日々の業務に追われて、最新<br>の設計手法を調査・学習する<br>機会が少ない。そのため非効<br>率な業務を行い続け、その性<br>でさらに学習機会が減るとい<br>う悪循環に陥っている。 | 様々な分野・企業様での、多種多様かつ最先端の開発経験を元に、お客様に適した設計方法や業務効率改善のご提案を行い、設計にかかる時間を減らしました。                                         |

| 検証   | 社内リソースが限られている<br>ため、複雑な検証を行うこと<br>が出来ない。だが、高品質も<br>同時に求めたい。                                      | 経験豊富なエンジニアが、第<br>三者検証及びランダム検証を<br>実施。通常の数十倍の検証を<br>行い、結果をお客様へフィー<br>ドバックすることで、高品質<br>を実現しました。                    |

| 品質   | 社外のエンジニアを交えてプロジェクトを行った際、言語・設計ルールなどがメンバー全員に浸透せず、手戻りが何度も発生してしまう。                                   | 設計ルールや情報の共有を周知徹底、あるいはフォーマット化することで、エンジニアの意識を統一。さらに、細かな問題にもエンジニアが迅速に対応することで、手戻りの発生を激減させました。                        |

| 納期   | 突然の納期短縮を、上層部から迫られた。                                                                              | お客様とスケジュールを共有<br>し、効率的な開発方法や開発<br>の優先順位をご提案。さらに、<br>スケジュール管理やリソース<br>の集中的投入などの組織的な<br>対応を行って、指定された期<br>日に納品しました。 |

# 大規模

## Cベース設計サービス(1)

プライムゲートでは、LSIの大規模化・複雑化に対応するために、C/C++/SystemCを利用しての開発に取り組んで参りました。

設計・検証に時間がかかりすぎたり、手戻りが多すぎて困っていませんか? 「忙しくて、SystemCを導入する余裕がない…」なんてことありませんか? その悩み、プライムゲートが解消します。

### Cベース設計のメリット

Cベース設計は、従来のHDLによる設計に比べ、以下のメリットがあります。

- ✓ 記述量が少なくて済む

- → **開発の高速化**が可能です。

- ✓ オブジェクト化に向いている → 資産の流用性が向上します。

- ✓ 高い抽象度での設計が出来る → 設計の効率が改善します

- ✓ アサーション等が利用しやすい → 検証の効率が改善します

### プライムゲートの方針

お客様のため、高品質・短納期での開発のため、そして業務効率改善のため。 プライムゲートは、Cベース設計に対して3つの方針を掲げています。

- 1. 各社の動作(高位)合成ツールに対応します。 (Catapult C, Cynthesizer, Cyber Work Bench, DesignPrototyper)

- 2. PV (Programmer's View), Untimed TLM に対応します。

- 3. 生産性の大幅改善を目指します。

なお、弊社の「画像動画処理用C言語のLSI化支援システム開発」が、経済産業省より、「平成21年度 戦略的基盤技術高度化支援事業」の認定を受けました。 本研究開発は開発時間短縮と生産性向上を主な目的とし、上記の方針を適用しております。その結果、**平均で2倍程度の生産性向上を達成**いたしました。

### 研究概要

- 1:C/C++/SystemCの、設計フェーズによる使い分け

- 2:各社動作合成ツールの、状況に合わせた効率的な利用

- 3:Cベース設計との親和性が高いSystemVerilogを検証に利用

- 4:ソフト/ハードIPの効率的な設計・蓄積・再利用手順を構築

# Cベース設計サービス(2)

### SystemCによる開発実績(一部)

プライムゲートは、様々なお客様のSystemCでの開発をサポートしました。 その実績は、一般的なSoC向けのモデル設計にとどまらず、高位(動作)合成 のサポートをはじめとした様々な作業範囲に広がっています。 ここでは、開発実績の一部をご紹介いたします。

プライムゲートなら、あらゆるフェーズでSystemC開発がサポート可能です。 仕様検討から全体的に、あるいは検証だけのワンポイントで。 お客様の状況に合わせて、プライムゲートのサービスをご利用下さい。

#### 仕様検討~設計・検証

1. 仕様設計からの参画、および動作合成用のSystemCモデルを作成 (アプリケーション:カメラ、抽象度:BCA/RTL)

#### 設計・検証

- 2. 支給された要求仕様書をもとに、動作合成可能なSystemCモデルを開発 (アプリケーション:テレビ、抽象度:RTL)

- 3. SystemCで作成したリファレンスモデルの検証 (アプリケーション:カメラ、抽象度:-)

#### 高位合成・等価検証

- 4. 高位合成向けの記述を行い、合成結果からRTLを作成 (アプリケーション:テレビ、抽象度:BCA/RTL)

- 5. SystemCモデルと動作合成結果の等価検証を実施 (アプリケーション:テレビ、抽象度:RTL)

#### パフォーマンス検討用モデル作成

- SoCのパフォーマンス検討用SystemCモデルの開発 (アプリケーション:(開示なし)、抽象度: OSCI TLM2.0)

- 7. システムアーキテクチャ検討用のSystemCモデル群の開発 (アプリケーション:(開示なし)、抽象度: OCP TL-2)

- 8. システムLSIのパフォーマンス検証用環境作成 (アプリケーション: OA機器、抽象度: OSCI TLM2.0)

#### その他

9. SystemC2.1 v1で記述されたコードのSystemC2.2へのコンバージョン (アプリケーション:通信機器 、抽象度: – )

## 検証サービス(1)

ASICやアンチヒューズFPGAといった、ミスの見落としが許されないデバイスでの開発。それを成功させてきたプライムゲートだからこその、質の高い検証サービスをご提供致します。

### 検証の手間を省く!検証自動化のご提案

開発が大規模化・複雑化するにつれ、検証の重要性は圧倒的に高まります。 それに伴い、開発期間全体に占める検証工数の割合や手戻りの可能性も増大 します。工数を抑え、無駄な手戻りを減らすには、検証の自動化が有効です。 プライムゲートでは、検証環境構築、検証実行、コンサルティングまで、お 客様の状況にあわせ、様々な形で検証自動化をご提案します。

#### 検証自動化の一例

✓ テストベンチ・オートメーション検証✓ カバレッジ・ドリブン検証✓ アサーション・ベース検証∴ 回路機能を自動火まック

### 検証を確実にする!第三者検証のご提案

検証の際に怖いのが、思い込みによる検証漏れやミス。設計者と検証者を分離すればその可能性は低下しますが、設計者と検証者を全く別にするには、そのためのリソース確保が必要になります。

そこで、思い切って、検証業務を外部に出してみてはいかがでしょうか。

# 検証サービス(2)

### 検証サービスの効果

検証項目を、第三者視点で客観的に抽出できます。

豊富な実績より、最適な検証手法をご提案できます。

質の高い検証ドキュメントが蓄積できます。

検証のゴールが明確です。

検証の進捗状況を定量的に把握可能です。

短期間での検証環境構築が可能です。

検証の妥当性が証明されるので、高品質化に役立ちます。

### 検証サービスの成果物一例

担当者以外でも理解できる検証仕様書

可読性と再利用性の高い検証環境や検証シナリオ

検証結果報告書では、様々な手法で検証結果の妥当性を証明

### 検証サービスの実績一例

#### **Specman Elite**

UVCを利用したバスシステムの検証

### **SystemC**

システムアーキテクチャ検討のためのモデル群開発

#### **SystemVerilog**

DDR-SDRAMのアドレス制御部のアサーション検証

### C/C++を利用した検証用モデル

画像系/通信系のビットストリーム生成モデル(入力モデル、期待値モデル)

# PRIMEGATE Ltd.